IOTA Crypto Core FPGA — Final Report

This is my final report of the IOTA Crypto Core project. In case you missed the last, click here.

Interesting 9 month of work coming to an end — Time to sum everything up!

Overview

PiDiver PoW

The first milestone was the PiDiver. This work was done before the Ecosystem funding was announced and I’m glad I could include it the proposal which gave me nice compensation for the work I’ve done!

There also is powsrv which is a PoW-as-a-service service for outsourcing PoW to highly specialized and efficient hardware based on the PiDiver.

IOTA Crypto FPGA Core

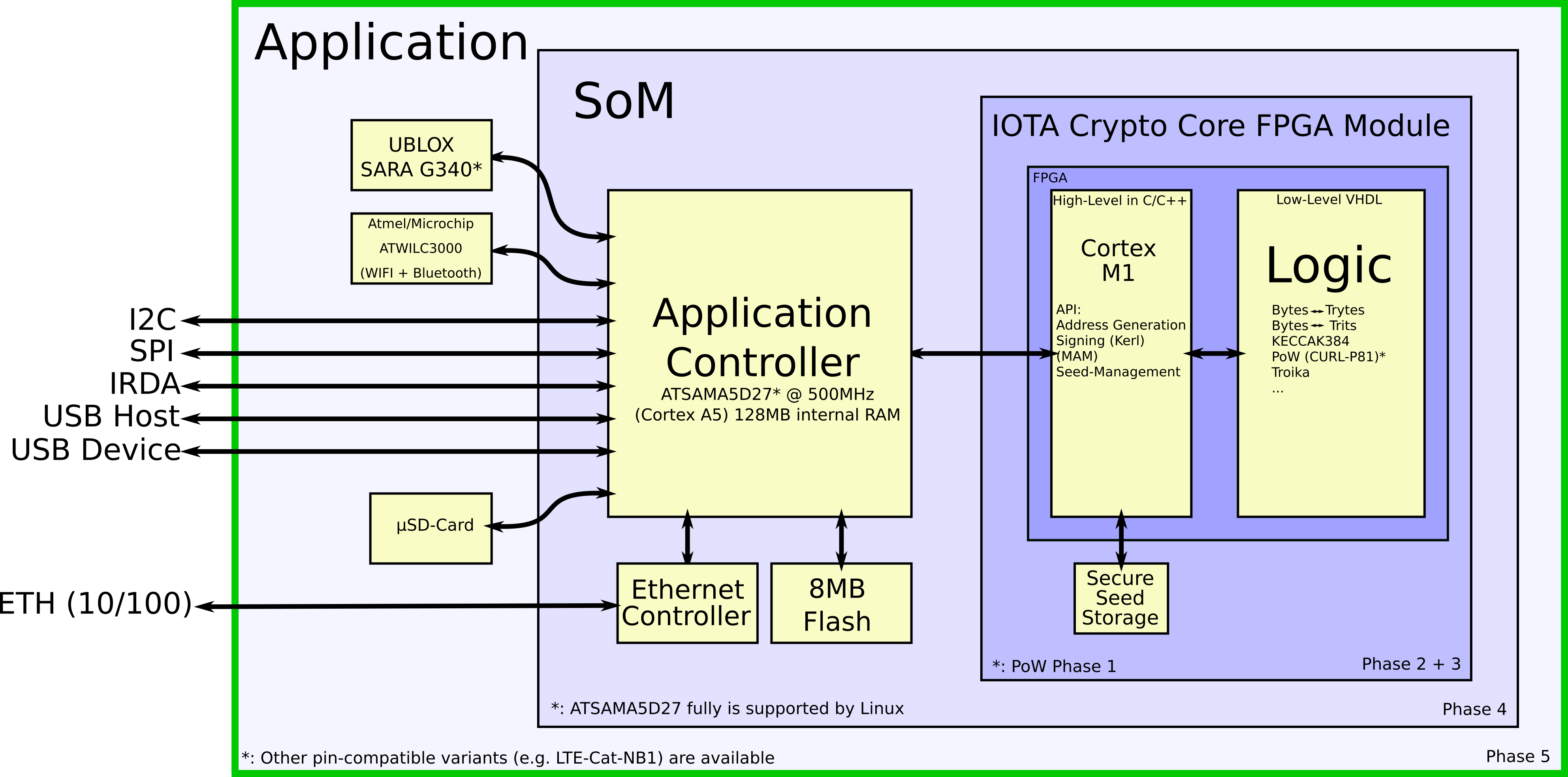

The second milestone (reports here, here and here) was the development of an FPGA core which provides most IOTA core functions with hardware acceleration. It offers a high-level API which is easy to use whereas computationally intense low-level calculations are off-loaded to specialized logic which gives significant advantage in speed compared to a software-only solution.

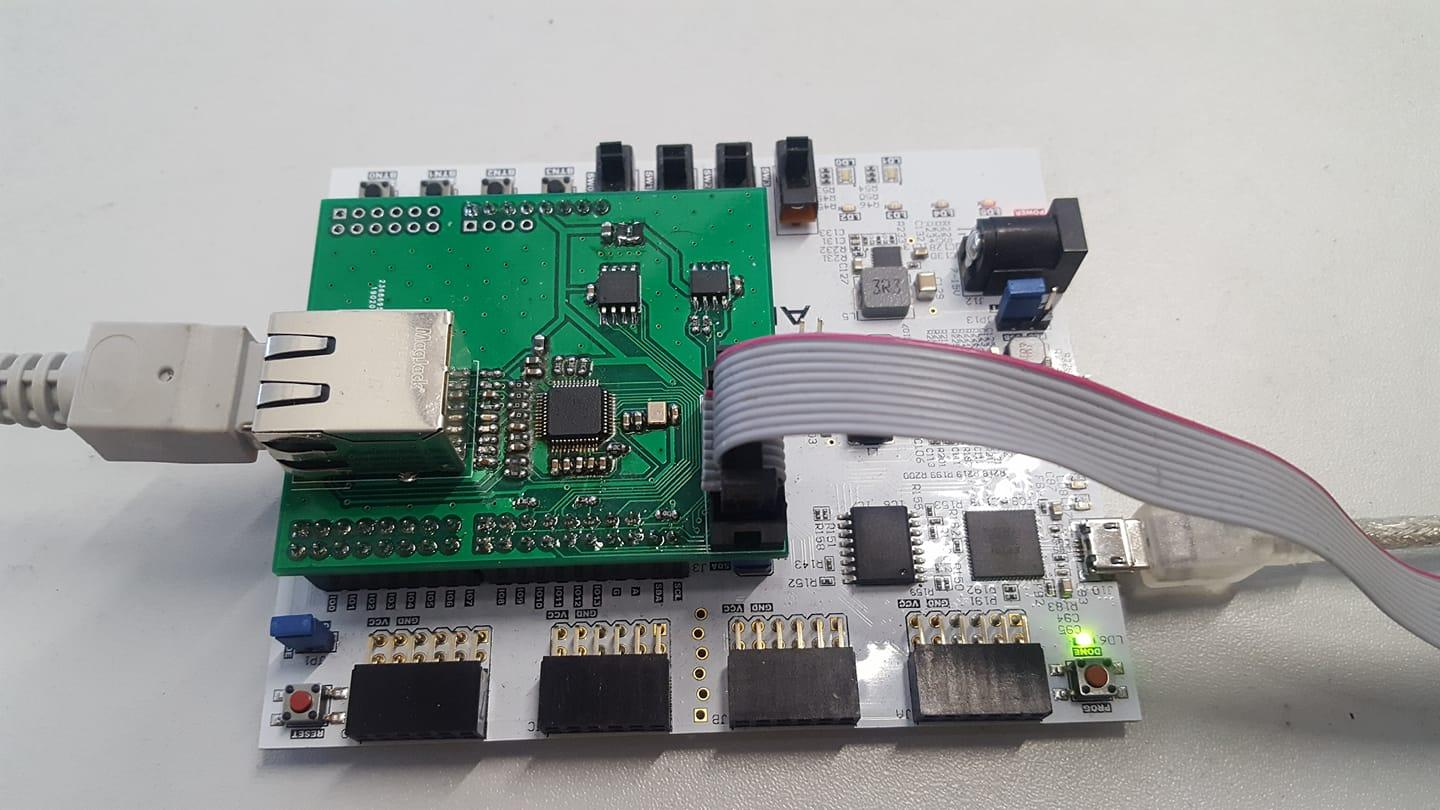

For this work, an off-the-shelf Arty S7 board was used and a HAT was designed. The HAT had a secure-element, SPI-Flash (was never used) and a W5500 ethernet controller on board.

Inside the FPGA, a Cortex M1 (ARM) soft-cpu is running (@ 100MHz) which can be programmed in C/C++. The firmware is protected by security mechanisms the FPGA provides. It should be hard for attackers to unauthorizedly gain access of seeds — which are stored in a secure-memory — or to tamper with the firmware.

Also inside the FPGA, there is specialized logic which accelerates hashing (Curl-P81 (and PoW), Keccak384 (used in Kerl) and Troika) and type conversions (binary <-> trinary). This specialized logic blocks are called hardware-accelerators and give a nice performance-boost (hashing >150) compared to software-only implementations. They often are faster than hashing running on a PC CPU with e.g. 3GHz (some speed-comparisions here and here).

IOTA Crypto FPGA Module

The next milestone (report here) was to build dedicated hardware for the FPGA core developed in the last milestone.

The result was a small (30x26mm) FPGA module which can be put in a mini-PCIe socket (but it’s not mini-PCIe!).