IOTA Pearl-Diver (PoW) Core in VHDL für Raspberry Pi

Updates:

2018-05-17: It’s alive *muahaha* It’s working fine and reaching about 14.5MH/s

2018-05-07: Some optimisations … Reaching 12.9MH/s on Altera DE1

2018-05-04: Installation instructions for Raspberry Pi added

2018-05-03: Major core optimizations – reaching now about 12MH/s.

Introduction

IOTA PoW needs a lot of computational power which makes sending transactions on smaller microcontrollers (like ARM) very slow. One of the main reasons is that the innerst loop of Curl-P81 can’t be computed very efficient on general purpose CPUs. Even modern CPUs with SIMD extension (like SSE or AVX) are heavily restricted when it comes to true parallel calculations.

This is a port of IOTA IRI’s Pearl-Diver for PoW-computation for FPGAs which speeds up the process of doing Proof-Of-Work significantly by a factor of more than 140 compared to e.g. a Raspberry Pi.

The core concept is that FPGAs are able to calculate one round of Curl-P81 in a single clock cycle and one complete Hash in about 85 (including test for valid nonce). The core works 5-fold which means, in every 85 clock cycles 5 Hashes are calculated in parallel – this gives about 12.87MHash/s at a clock frequency of 220MHz. Moreover, the parallel computation can be adjusted easily to be even faster on larger FPGAs.

For instance, finding the nonce of a single transaction takes about 90s on a Raspi. Finding the nonce hardware accelerated by this core reduces the time to ~350ms.

This core can be also used by IRI when using a modified version which allows to use dcurl as external hashing libary.

So it is possible to build a full-node on raspberry pi with a decent hashing power for doing PoW calculations.

The project aims to be completly open source including all source codes, schematic, layouts.

VHDL-Core

The IOTA PoW Pearl-Diver core was implemented in VHDL.

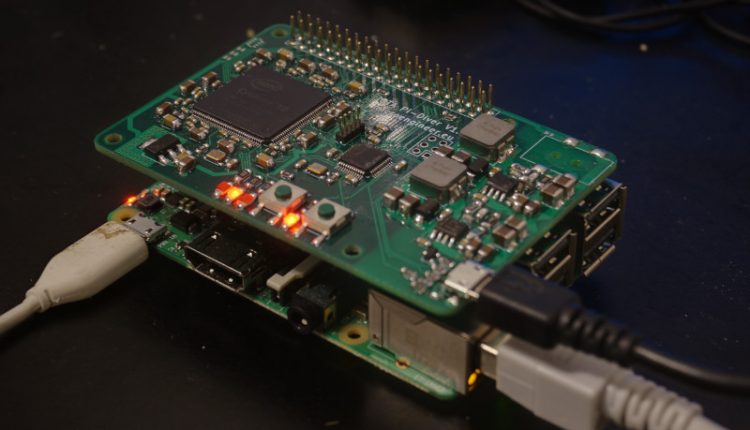

Following an image showing my proof-of-concept prototype using an older Altera DE1 (Cyclon 2 with 20kLE).

Except an Altera PLL, no additional core or unusual VHDL library is used which makes it very simple to implement for other FPGA platform targets.

Moreover the core is customizable so the 5-fold parallelization can be increased or reduced (currently up to 8 but that could be changed with little work) depending on the resources of a FPGA target.

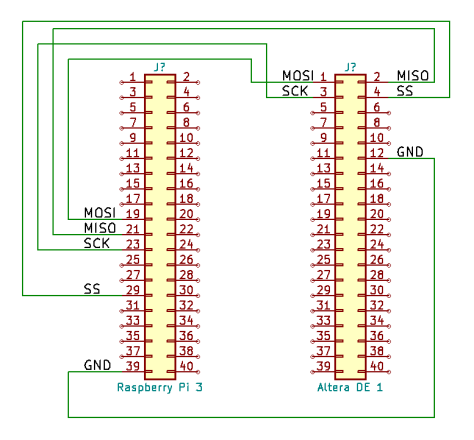

The core implements a high-speed SPI interface which directly can be used by the hardware SPI of a Raspberry Pi.

Following the electrical connections between Altera DE1 and Raspberry Pi.

Here the synthesis report for the EP2C20:

Maximum clock frequency:

First clock is I/O like SPI and commando decoder (running @ 110MHz in the design). Second clock is the actual Pearl-Diver PoW State-Machine reaching 220MHz.

Design is still functional although all of the optimizations 🙂

Pearl-Diver Core Repository

Following repository not only contains VHDL source but also an Altera DE1 project file and an output file which can be loaded directly into the board:

Link to Open-Cores project site

Or on Github (without Account necessary):

Hashing-Library dcurl with FPGA support

dcurl is a very fast Curl-Hashing-Library which not only supports graphics cards (OpenCL) but also provides highly optimized variants for SSE and AVX capable CPUs.

I did a fork of the library and added code for support of the VHDL Pearl-Diver.

The advantage is that every software working together with dcurl library can make use of the FPGA version of Curl (on Raspberry Pi – for different targets the low level control of SPI has to be replaced).

Compiling and Testing with dcurl

1. Download and install BCM2835 library

# download the latest version of the library, say bcm2835-1.xx.tar.gz, then: tar zxvf bcm2835-1.xx.tar.gz cd bcm2835-1.xx ./configure make sudo make check sudo make install

2. Enable „SPI“ under „Interfacing Options“.

sudo raspi-config

3. Load kernel module with modprobe

sudo modprobe spi_bcm2835

4. Check Permissions

pi@raspi:~ $ ls /dev/spidev0.0 -al crw-rw---- 1 root spi 153, 0 May 3 15:17 /dev/spidev0.0 pi@raspi:~ $ groups pi adm dialout cdrom sudo audio video plugdev games users input netdev gpio i2c spi

5. Clone and Compile dcurl library

git clone https://github.com/shufps/dcurl cd dcurl make BUILD_FPGA=1

6. Test library (for a reason I still don’t know SPI access only with „sudo“ possible).

cd build sudo ./test-pow_fpga parallel level detected: 5 Found nonce: 000c9b9c (mask: 00000008) Time: 321ms - MH/s: 12.870

7. If there is no error then everything worked 🙂

Prototyp für Raspberry Pi

One of the main goals was to developent a PCB with FPGA for PoW which fits perfectly on the top of a Raspberry Pi.

The PCB is equipped with a modern FPGA (Cyclon 10 LP, 10CL025) which also has a bit more resources than the older Cyclon 2. This resources are sufficient to extend the internal 5-fold calculations to 7-fold @ 175MHz. Alghouth the overall-speed is slightly higher (~14MH/s) energy consumption is much less compared to the proof-of-concept because Cyclone 10 LP is a low-power device – so improving Hash/Watt a lot.

Following the cad-image of the designed PCB (please don’t get confused about the couple of missing 3d-models^^):

Additionally the board can be used with Raspberry – or without. It also has got an ARM controller on board – so the board can directly be used with USB.

And here the real protype:

As estimated, the core is faster on Cyclone 10 because the FPGA has more resources:

parallel level detected: 7 Found nonce: 000c9b9c (mask: 00000008) Time: 397ms - MH/s: 14.569

Schematic-, Layout-, BOM-Files

Not yet – but I promise as soon as the PCB is back from the manufacturer and it works 🙂

Current Project State

- Proof-Of-Concept (Done)

- PCB designed (Done)

- PCB ordered (Done)

- PCB assemblied and tested (DONE)

Support

This project consumed a lot of work and time and financial resources. I would be very happy if some people would consider to leave a small donation:

LLEYMHRKXWSPMGCMZFPKKTHSEMYJTNAZXSAYZGQUEXLXEEWPXUNWBFDWESOJVLHQHXOPQEYXGIRBYTLRWHMJAOSHUY

In order to protect my work – except dcurl of course – it is licensed under a non-commercial open-source license.

The project will become completely GPL (which allows commercial use) when the IOTA address above shows a balance of >1000MIOTA. (Or if IOTA Ecosystem Fund for which I applied is granted 🙂 )

Licence

Everything on this side will be available for download (software, schematic, board files, BOM, …)

Currently: Attribution-NonCommercial 4.0 International (CC BY-NC 4.0) (please look under „Support“).